Delta‑L 4.0을 이용한 PCB 신호 구조의 삽입 손실 테스트

데이터 속도가 계속 빨라짐에 따라 고속 디지털 설계의 신호 무결성 측정이 더욱 어려워지고 있습니다.

데이터 속도가 계속 빨라짐에 따라 고속 디지털 설계의 신호 무결성 측정이 더욱 어려워지고 있습니다.

예를 들어 PCIe 5.0은 최고 32 GT/s의 데이터 속도를 제공하며, RC(Root Complex)와 EP(End Point) 간 최대 삽입 손실 예산을 정의합니다. 이 삽입 손실은 RC 패키지, EP 패키지, 커넥터, 전극 외에도 주로 해당 PCB 계층의 신호 트레이스에 따라 달라집니다. 따라서 인치당 삽입 손실이 핵심 지표이며, PCB 프로브, 전극과 같은 lead-in, lead-out의 효과를 제외하고 측정해야 합니다. Delta L은 이러한 효과를 제외하고 각각 다른 길이의 테스트 쿠폰 측정으로 도출된 PCB 트레이스의 인치당 삽입 손실을 계산하는 간단한 방법을 제공합니다.

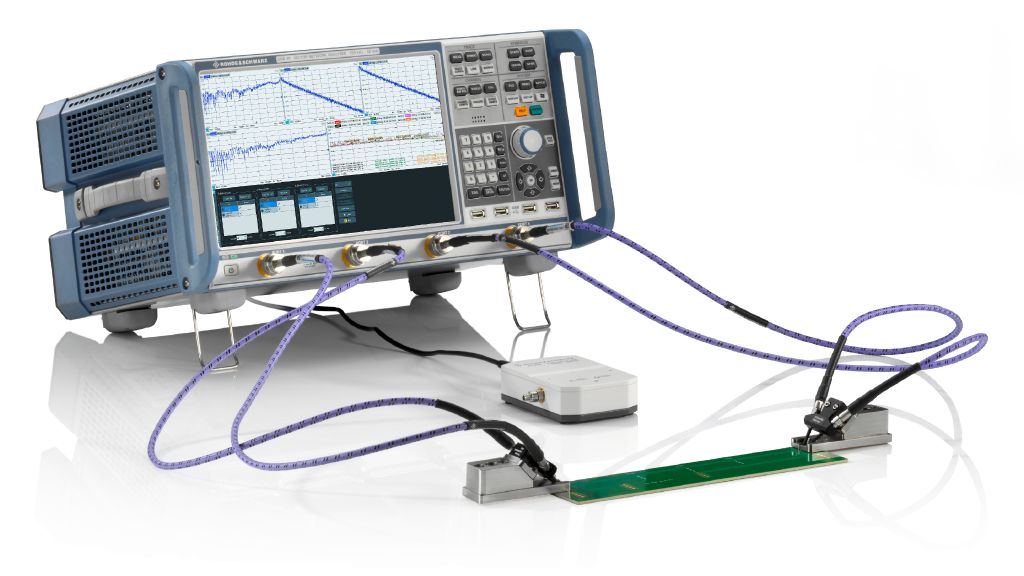

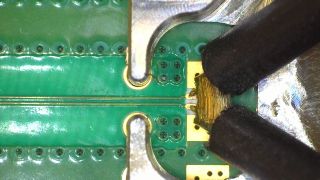

그림 1: Delta‑L 4.0 프로브를 이용한 R&S®ZNB40 셋업

PCB 신호 트레이스의 인치당 삽입 손실 검증용

특정 PCB 계층에서 신호 트레이스의 삽입 손실을 측정할 때에는 PCB 프로브, 전극을 포함한 lead-in과 lead-out이 결과에 불필요한 왜곡을 일으키므로 관련 영역까지의 값을 측정에서 제거해야 합니다. Delta L은 이러한 효과를 수학적으로 제거하고 다른 길이의 신호 구조를 사용해 특정 PCB 계층에 있는 신호 트레이스의 인치당 삽입 손실을 계산하도록 개발되었습니다. Delta L 측정 워크플로우는 R&S®ZNx-K231 옵션으로 R&S®ZNA, R&S®ZNB, R&S®ZNBT, R&S®ZND Vector Network Analyzer에 완벽히 통합됩니다.

이 기술은 테스트 픽스처의 완전한 특성분석과 해당 테스트 픽스처의 디임베딩은 VNA(Vector Network Analyzer)의 기준면을 DUT(Device under Test) 옆의 새로운 위치로 완전히 이동시킵니다. 이 방법은 모든 유형의 DUT를 측정하는 데 사용할 수 있습니다. 반면 Delta L 알고리즘은 DUT가 특정 PCB 계층(길이 및 손실 특성으로 구별)에서 준-최적 전송 라인에 있는 것으로 가정합니다. 전체 테스트 픽스처 특성분석 및 디임베딩 워크플로우는 R&S®ZNA, R&S®ZNB, R&S®ZNBT, R&S®ZND Vector Network Analyzer에서도 지원됩니다. 해당 옵션은 R&S®ZNx-K210 (EZD), R&S®ZNx-K220 (ISD), R&S®ZNx-K230 (SFD)입니다.

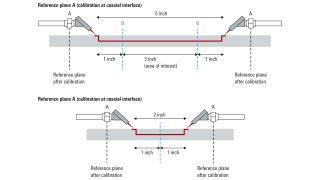

특정 PCB 계층에서 인치당 삽입 손실만 확인하려는 경우 Delta L은 세 가지 방법(1L, 2L 또는 3L)으로 PCB 구조를 측정하여 해당 결과를 얻을 수 있는 직관적, 맞춤형 방법을 제공합니다. 즉, 각각 다른 테스트 길이가 다른 테스트 쿠폰의 수를 정의합니다. 그림 2는 5인치 및 2인치 테스트 쿠폰을 사용하는 2L의 예제입니다.

Delta L 3.0은 프로브, 프로브 론치 및 피치(1.0mm), 인치당 삽입 손실을 계산하는 알고리즘을 정의합니다. PCIe 4.0 및 최대 20 GHz 주파수까지 지원합니다. Delta L 4.0은 PCIe 5.0 및 PCIe 6.0에 맞게 최근 확장된 버전으로, 프로브 론치 및 피치(0.5mm)를 재정의하며 알고리즘을 최대 40 GHz까지 확장합니다. R&S®ZNx-K231 옵션에는 Delta L 4.0 및 Delta L 3.0 측정에 사용 가능한 새로운 Delta L 4.0 알고리즘이 포함되어 있습니다.

그림 2: 두 가지 길이의 테스트 쿠폰을 사용하는 Delta‑L 방식

그림은 5인치 및 2인치 테스트 쿠폰. 인치당 삽입 손실은 관련 영역에 대해 결정되며, 이 그림에서는 5인치 테스트 쿠폰에 3인치 트레이스 세그먼트가 포함되어 있습니다.

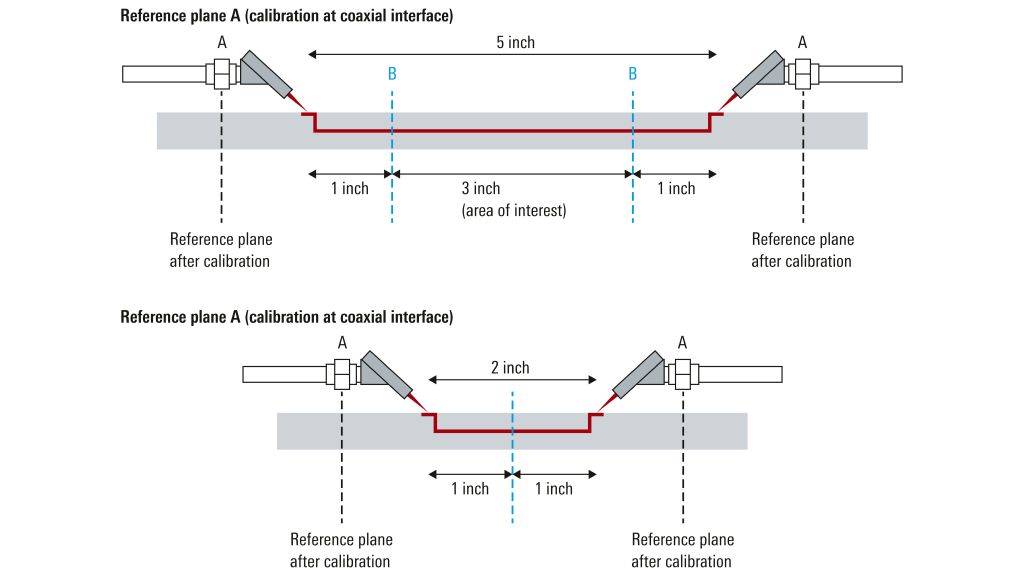

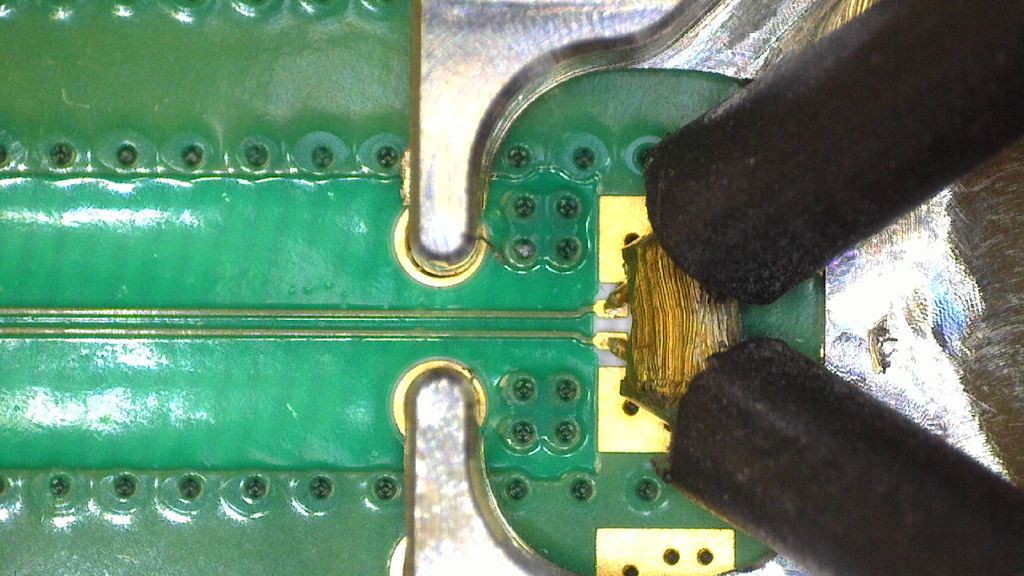

그림 3: PacketMicro의 Delta‑L 4.0 프로브

테스트 보드에 가이드 핀이 꽂혀 있고 10", 5", 2" 테스트 쿠폰이 각각 다른 PCB 계층에 있는 Delta‑L 4.0 프로브

그림 1은 전반적 셋업, 그림 3은 사용한 Delta L 4.0 프로브와 테스트 보드를 확대한 사진, 그림 4는 프로브 론치를 더 크게 확대한 사진입니다. VNA는 (예를 들어 자동 calibration 유닛인 R&S®ZN-Z54를 사용해) 동축 케이블의 끝까지 calibration 합니다.

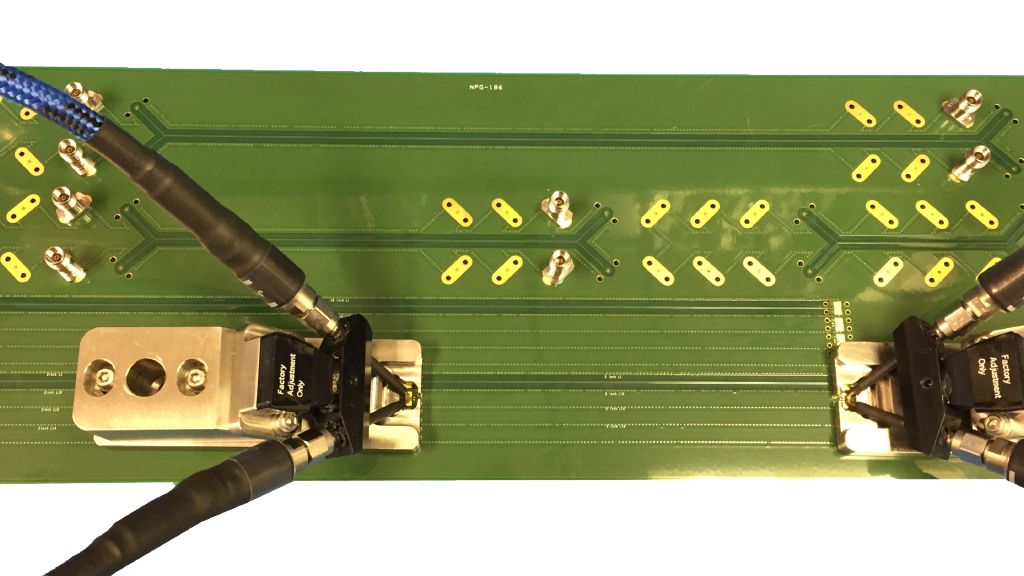

그림 4: PacketMicro의 Delta‑L 4.0 프로브 및 테스트 보드

Delta‑L 4.0 프로브 론치를 나타냅니다. Delta‑L 4.0은 0.5 mm 피치의 GSSG(Ground-Signal-Signal-Ground) 구조를 정의하여 Delta‑L 3.0의 1.0 mm 피치를 대체합니다.

R&S®ZNx-K231 옵션을 사용하면 Delta L 워크플로우를 R&S®ZNA, R&S®ZNB, R&S®ZNBT, R&S®ZND Vector Network Analyzer에 완벽히 통합할 수 있습니다. 이 구현 방식에서는 1/2/3가지 길이의 테스트 쿠폰을 사용하는 1L, 2L, 3L 방식을 지원합니다. 기기 내에 통합할 경우 외부 PC에서 후처리해야 할 필요가 완전히 없어집니다.

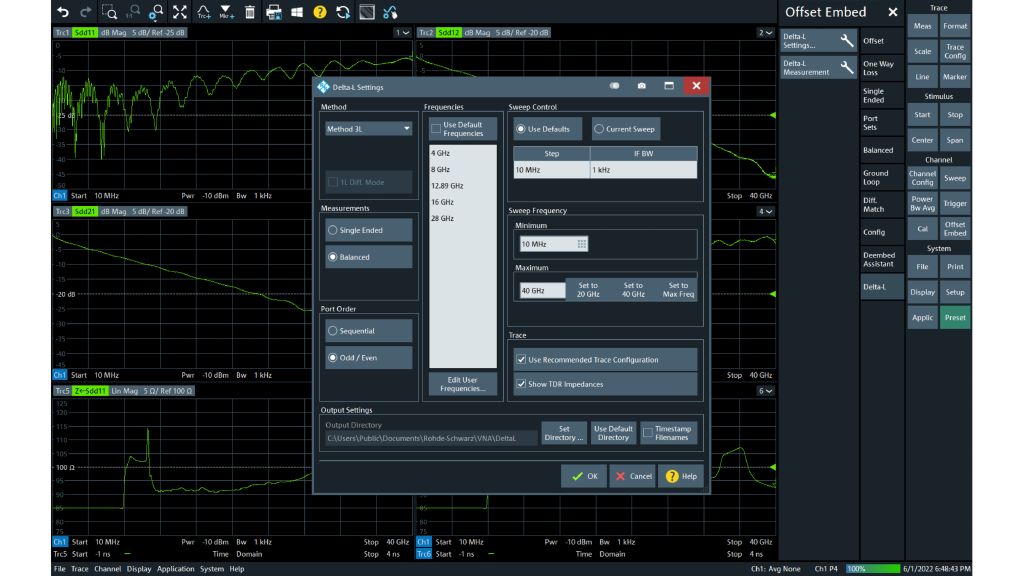

그림 5: R&S®ZNx-K231에 Delta‑L 구현

이 구현 방식은 1L, 2L, 3L 측정 방식을 지원합니다.

그림 5 및 그림 6에 나와 있는 대화상자를 통해 기기의 포트 구성, Delta L 방식 선택, 스윕 정의를 포함한 Delta L 측정 설정에 액세스할 수 있습니다. S-파라미터 이외에 TDR 임피던스도 표시하여 Delta L 프로브의 정상 연결 상태를 검증하고, 필요 시 프로브를 재조정할 수 있습니다.

사용자가 설정을 정의하면 Delta L 측정을 시작하여 사용자에게 Delta L 워크플로우의 각 단계를 안내할 수 있습니다. 사용자는 각 쿠폰 길이에 대해 실시간 측정을 선택하거나 Touchstone 포맷에 정의되어 있는 기존 측정 결과를 로드할 수 있습니다.

그림 7은 10", 5", 2" 테스트 쿠폰을 사용하는 3L 방식의 예를 보여줍니다. 이 경우 Delta L 알고리즘은 해당 lead-in과 lead-out을 제거하고, 그림 2의 설명과 같이 10"와 5" 결합(교차 영역 = 5"), 10"와 2" 결합(교차 영역 = 8"), 5"와 2" 결합(교차 영역 = 3")으로 인치당 삽입 손실에 대한 세 가지 결과를 제공합니다. 3L 방식은 가장 많은 정보를 제공하며 초기 단계(예: 소재 선택)에서 일반적으로 사용되는 방식입니다.

그림 8은 10인치 및 5인치 테스트 쿠폰을 사용하는 2L 측정의 예를 보여줍니다. 여기에서 Delta L 알고리즘은 해당 lead-in과 lead-out을 제거하고 사용 가능한 길이인 10" 및 5"(교차 영역 = 5")를 결합하여 인치당 삽입 손실에 대해 하나로 결합한 결과를 제공합니다. 2L 방식은 관련 영역의 정확한 인치당 삽입 손실 결과를 제공하며 보드 샘플링에 대해 권장하는 방식입니다. 1L 방식은 한 가지 쿠폰 길이만 사용하며 측정 결과에서 lead-in 및 lead-out을 제거하지 않습니다. 이 방식은 양산용 테스트를 위해 설계되었으며, 복수 보드의 테스트 쿠폰에 대한 제조 공정의 추세와 통계를 제공합니다.

필요한 전체 테스트 쿠폰의 측정 결과가 확인되는 즉시 Delta L 워크플로우에서 Run 버튼을 사용해 해당 Delta L 계산을 시작할 수 있습니다. 결과는 새로운 추가 다이어그램에 표시됩니다. Delta L 측정 설정에서 선택한 모든 주파수에 대해 인치당 삽입 손실 및 해당 불확도의 수치값을 나타내는 마커가 제공됩니다. 그림 9는 10" 및 5" 테스트 쿠폰을 이용한 2L 방식의 Delta L 결과를 나타냅니다. 주황색 트레이스는 평활화된 곡선을 나타내며 선택한 주파수에 마커값이 표시되어 있습니다. 청색 트레이스는 기준 및 비교 대상에 대해 평활 처리되지 않은 곡선을 나타냅니다.

R&S®ZNA, R&S®ZNB, R&S®ZNBT, R&S®ZND Vector Network Analyzer는 기기 한 대로 디지털 고속 신호 구조에 대한 신호 무결성 테스트를 수행하는 데 필요한 모든 기능을 제공합니다. R&S®ZNx-K231 옵션에는 PCIe 5.0 및 PCIe 6.0에 필요한 최대 Delta L 4.0의 Delta L 측정 워크플로우가 포함되어 있습니다. Delta L 4.0은 최대 40 GHz용으로 개발되었으며, 특정 PCB 계층에 있는 트레이스 섹션의 인치당 삽입 손실을 구하는 간단한 맞춤형 방식을 제공합니다.

| 유형 | 타입 | 주문 번호 |

|---|---|---|

| Delta‑L 4.0 PCB 특성분석, Intel Delta‑L 4.0 방법론 기반 전체 1L, 2L, 3L 분석 | ||

| R&S®ZNA용 | R&S®ZNA-K231 | 1339.3922.02 |

| R&S®ZNB용 | R&S®ZNB-K231 | 1328.8628.02 |

| R&S®ZNBT용 | R&S®ZNBT-K231 | 1328.8663.02 |

| R&S®ZND용 | R&S®ZND-K231 | 1328.8705.02 |