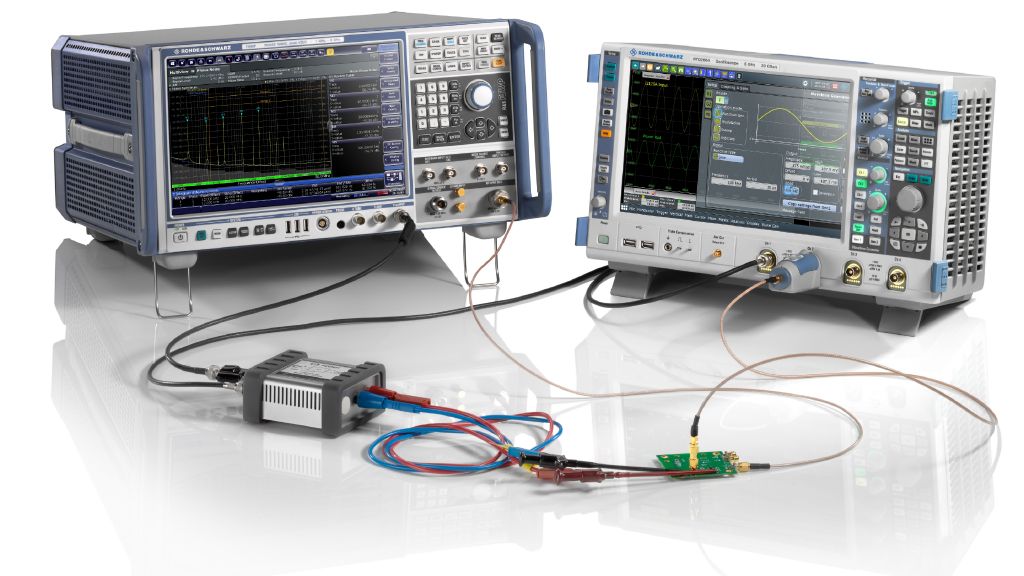

Measuring power supply induced jitter and PSNR in low jitter oscillators and clocks

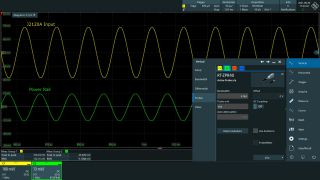

Timing components such as low jitter oscillators and clocks are necessary to facilitate increasing data rates in high speed digital designs. As part of the overall system design, the components also have to perform in the system’s non-ideal power integrity environment and limit the power supply induced phase noise and jitter from power rail disturbances. Measuring the power supply noise rejection (PSNR) requires accurate generation and leveling of artificial, sinusoidal disturbances and measurement of resulting phase-noise and jitter impairments.