Análise de designs de potência para SoCs de alta velocidade com conversores buck multifásicos

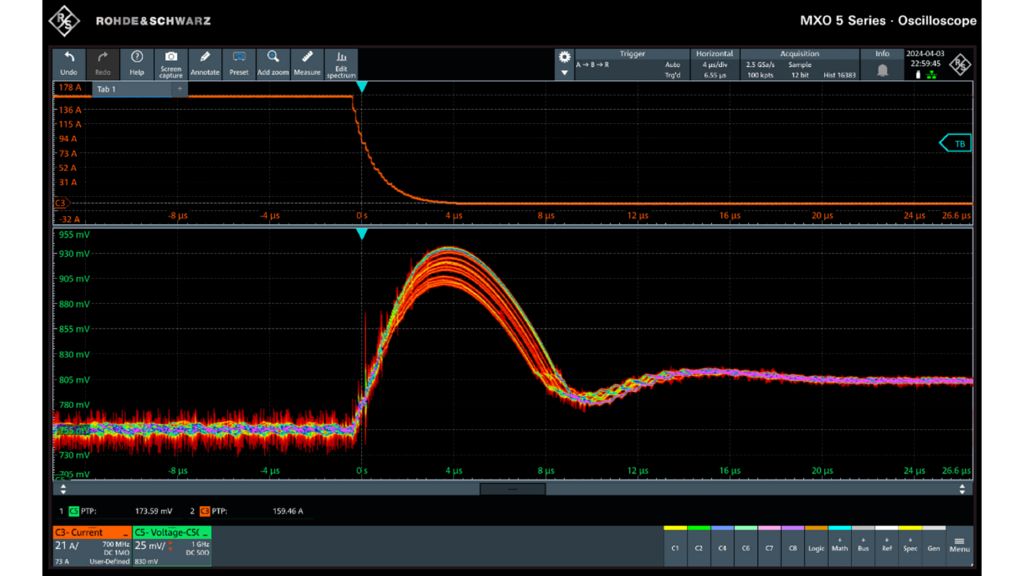

Mais funções, maior capacidade de processamento e taxas de transmissão de dados mais altas tornam o desenvolvimento de designs de potência dos SoCs (sistema em um chip) de alta velocidade um desafio. O número cada vez maior de trilhas de corrente que fornecem os vários blocos de função dos GPUs, FPGAs, ASICs e CPUs modernos exige um sequenciamento preciso durante a inicialização e o desligamento. Os níveis de tensão de alimentação também são reduzidos para diminuir a dissipação de energia dentro do SoC. Os requisitos de integridade de potência são mais rigorosos e é necessária mais corrente de alimentação nas trilhas de corrente. Os conversores buck multifásicos continuam a se tornar mais populares para trilhas de alta corrente. Os conversores têm muitos benefícios, mas os desenvolvedores também enfrentam desafios no que diz respeito ao design de potência e aos testes de validação.