Verifizierung auf Systemebene und Debugging von DDR3/DDR4-Speicherdesigns

Diese Application Note bietet eine Einführung in die DDR-Speichertechnologie sowie eine Erläuterung häufiger Herausforderungen aufgrund der besonderen Beschaffenheit von DDR-Daten, Befehl-/Adress- und Steuerbussen. Zudem werden gängige Messungen bei der Verifizierung und beim Debugging von DDR-Systemen beschrieben.

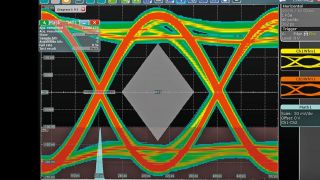

Das Dokument erläutert die empfohlenen Messpunkte und den Anschluss von Oszilloskop-Tastköpfen sowie die Kompensation der Effekte von DDR-Interposern mithilfe von Deembedding. Die Application Note beschreibt die Verifizierung der Signalintegrität mittels Augendiagrammmessung und hochentwickelten Trigger- und TDR-/TDT-Funktionen. Aufgrund der hohen Anzahl an Signalleitungen und der dynamischen Busterminierung wirkt sich SSN (Simultaneous Switching Noise) erheblich auf das DDR-Speicherdesign aus. Signalintegrität und Power Integrity hängen zudem stark vom Pattern ab. Das Dokument beschreibt Technologien zur Erreichung hoher Erfassungsraten ein und unterstützt bei der sicheren Erkennung von Worst-Case-Szenarien, die sich auf die Leistung des gesamten Speicherdesigns auswirken. Das Thema Power Integrity wird in diesem Dokument ebenfalls näher beleuchtet.

Mit Best-Practice-Beispielen für Design-Verifizierung und -Debugging richtet sich dieses Dokument an alle Systementwickler und Testingenieure, die DDR-Speichersysteme designen.