ローデ・シュワルツのソリューション

R&S®FSWP 位相雑音アナライザ/VCOテスタは、業界最高の位相雑音感度を備えています。さらにこれを、R&S®FSWP-B60 相互相関法オプションおよびR&S®FSWP-B61 相互相関法(低位相雑音)オプションによって向上させることができます。

R&S®FSWP-B64 残留位相雑音測定オプションを追加すれば、測定器に超低位相雑音信号源が内蔵され、相加性位相雑音測定を容易に実行できます。

あるいは、R&S®SMA100B RF/マイクロ波信号発生器のような外部信号源を使用して、テスト対象のPLLをシミュレートすることもできます。R&S®SMA100Bは最高の信号純度と位相雑音性能を実現していて、さまざまな位相雑音性能オプションにより性能拡張も可能です。

ほとんどのSerDes PLLおよびクロックシンセサイザーに対して、R&S®FSWP-B64およびR&S®SMA100Bの位相雑音は、DUTの相加性位相雑音と比較して無視できる程度の大きさです。R&S®FSWPによって測定された位相雑音は、主にDUTの相加性位相雑音を表しています。

R&S®FSWP-B64が採用している相加性位相雑音手法では、入力信号の位相雑音の影響をさらに大幅に縮小できます。他社製のソリューションとは異なり、手動で外部移相器との直交性を実現する必要はありません。R&S®FSWPは自動的にこれを行い、使いやすい位相雑音測定の新しい基準を打ち立てています。

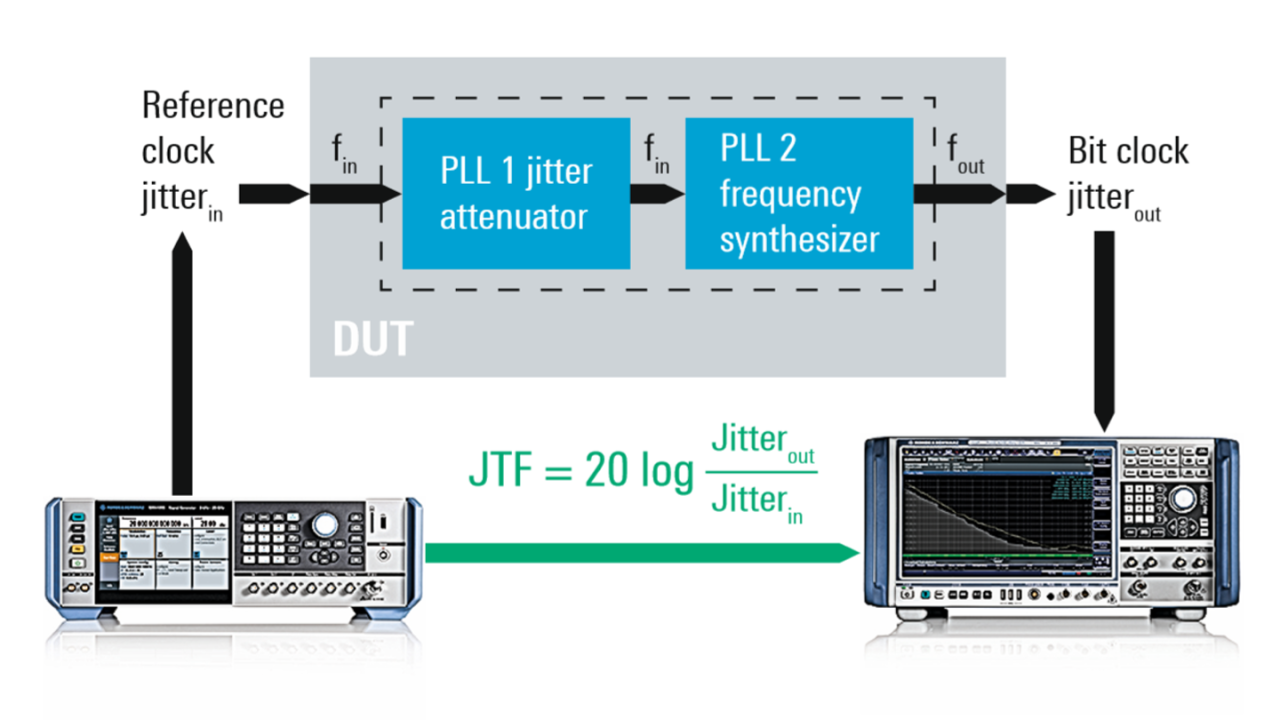

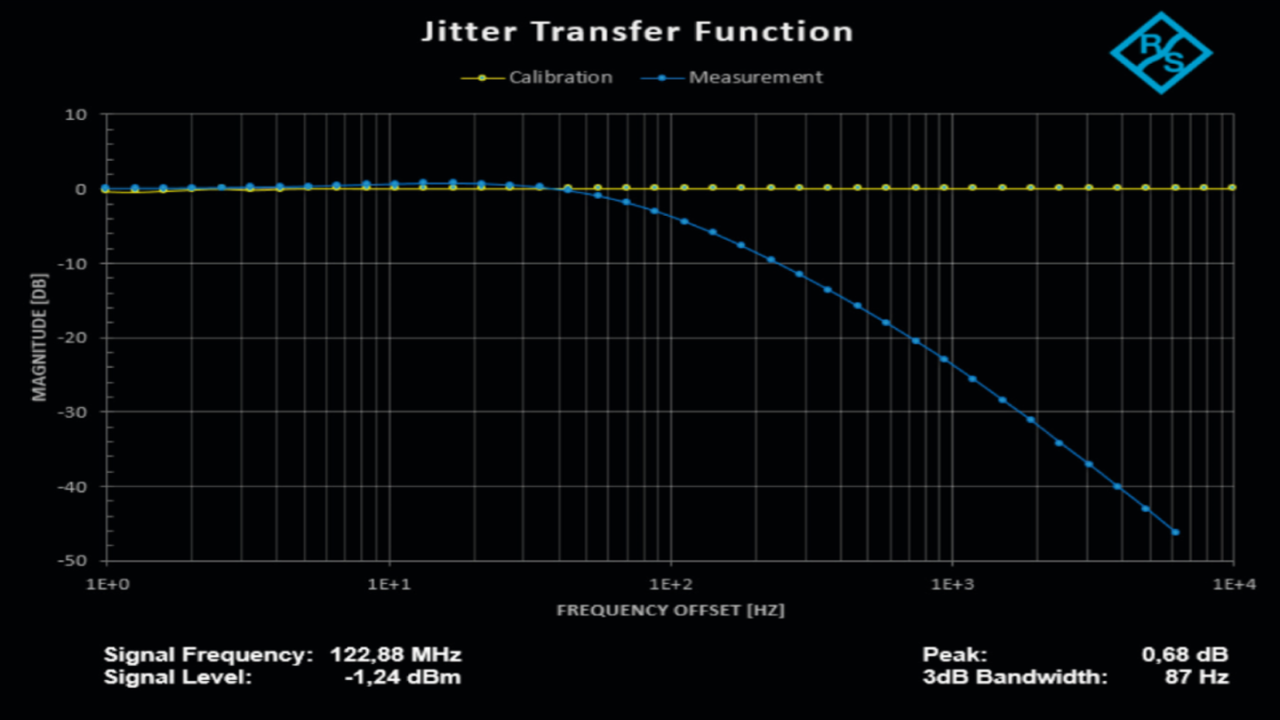

R&S®SMA100Bは、PLLのジッタ伝達関数の測定にも使用できます。PM変調(R&S®SMAB-K720 オプション)を介して、人為的なジッタが信号源に追加されます。

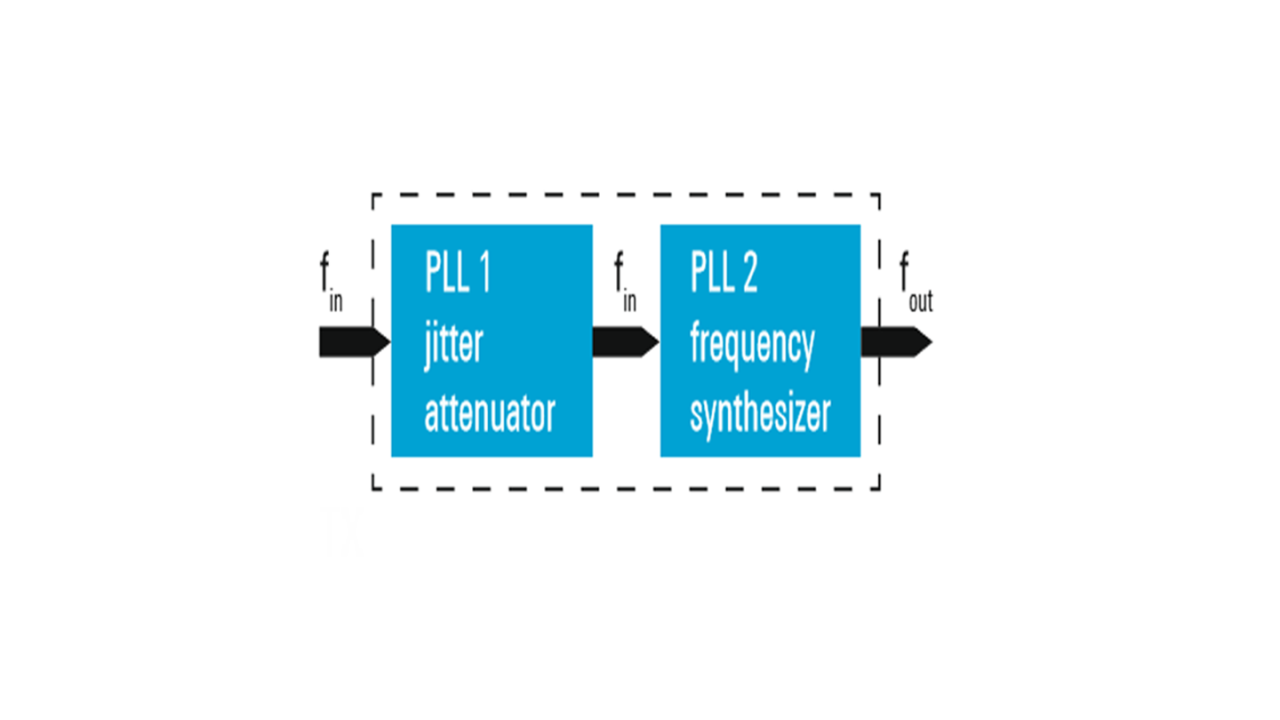

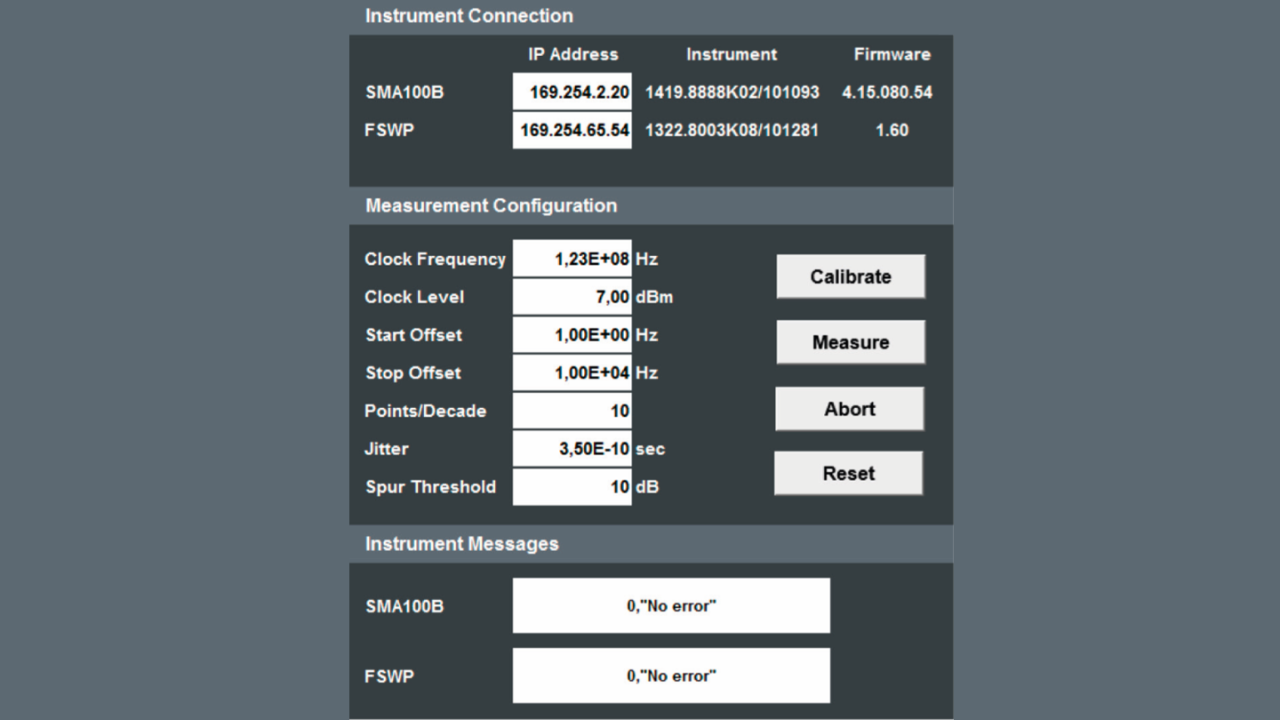

R&S®FSWPはDUT出力で実際のジッタを測定して、DUT入力でのジッタに対してそれをノーマライズし、ジッタ減衰を特定します。このアプリケーションカードのダウンロードセクションに外部ツールがあります。R&S®SMA100B(R&S®SMAB-K720オプションが必要)とは別に、R&S®FSWP(R&S®FSWP-B60またはR&S®FSWP-B61オプションが必要)とR&S®FSPNをサポートします。ツールは、さまざまな周波数オフセットでジッタ減衰を測定し、ピークや3 dB帯域幅を含む、DUTのジッタ伝達関数を提供します(下のスクリーンショットを参照)。