R&S®RTPによるリアルタイムディエンベディング

ディエンベディングは頻繁に必要となる複雑な作業ですが、ハードウェア/ソフトウェア統合ソリューションを使用すれば容易になります。

ディエンベディングは頻繁に必要となる複雑な作業ですが、ハードウェア/ソフトウェア統合ソリューションを使用すれば容易になります。

信号の測定に使用される信号経路、プローブ、ケーブル、フィクスチャ、およびその他のアクセサリの影響を軽減して、デザインの真の性能を検証すること。

DDRやPCIeのような高速インタフェースをデバッグする場合や、高速クロックを評価する場合や複雑なRF信号を解析する場合においても、テストセットアップによる負荷や反射などの影響を取り除いた、実際の信号を観察することが重要です。非理想的な信号経路の影響(減衰、スキュー、負荷など)を除去するプロセスは、ディエンベディングと呼ばれます。

リアルタイムオシロスコープでこのような歪みを除去するためには、一般的に、信号経路の影響を補正する応答を持つフィルターが必要です。このフィルターを波形に適用することで、アイの高さの増加、立ち上がり時間の短縮、反射の除去といった信号品質の改善が期待できます。

ただし、この方法には潜在的な問題がいくつかあります。

リアルタイムディエンベディング・アーキテクチャー

リアルタイムディエンベディング・アーキテクチャー

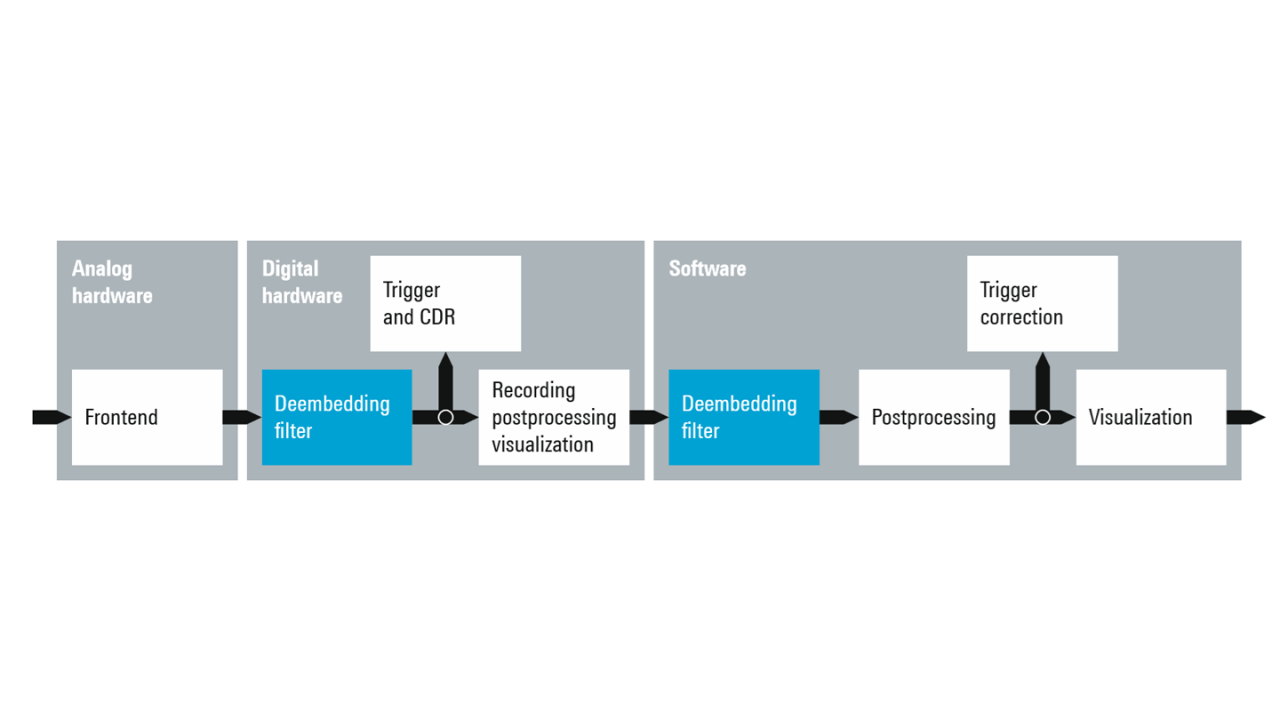

R&S®RTP 高性能オシロスコープは、このようなトレードオフに対処し、シンプルで高速なディエンベディングソリューションを実現するために設計されました。個々の回路素子の複数の周波数応答表示と、システム全体の応答を利用することで、帯域幅を最適化し、ノイズの増幅を最小限に抑えることができます。

R&S®RTPのディエンベディングフィルターは、A/Dコンバーターの直後にハードウェアで実現されています。この波形データのリアルタイム処理によって、フィルターを適用しても最高の更新レートを維持できます。プロトコルエラーのトラブルシューティングでも、アイダイアグラムのモニターでも、高速で応答性の高い測定システムを使用することで、重要な詳細情報を見逃すことがなくなります。

カスケード接続された信号トレースのディエンベディング

高速差動インタフェーステストの代表的な信号トレース構造は、位相整合の取れたケーブルセット、アダプター、テストフィクスチャから構成されます。ケーブル、アダプターなどのアクセサリは2ポートSパラメータでモデル化されるのに対して、フィクスチャは2ポートまたは4ポートのSパラメータで表されます。ディエンベディングアプリケーションは、各ブロックの入力/出力負荷を考慮しながら、Sパラメータのカスケード接続プロセスをシームレスに管理します。

優れたトリガ機能と高速なシグナルインテグリティー結果

ディエンベディングの最終段階では、フィルターを作成して、測定対象の信号に適用します。R&S®RTPでは、ディエンベディングフィルターが、デジタルトリガや高性能収集システムから利用できます。これにより、業界で初めてのディエンベディングトリガが実現されます。観察しているのと同じ補正済み信号でトリガできるのです。ハードウェアベースのディエンベディングにより、重要な波形処理も高速化されます。例えば、アイダイアグラムの更新速度は、他の測定器に比べて最大1,000倍も高速です。

アイマージンの改善

デザイン/テストエンジニアにとって最も一般的な課題の1つは、設計した製品の真の性能を知ることです。言い換えれば、測定が実際の性能を反映しているのか、それともテスト機器の負荷、コネクタの反射、ケーブル損失、あるいはその他さまざまなテスト機器の不完全さが結果に影響しているのかということです。これらの既知の不完全さに関しては、ディエンベディングの技法を用いることでデザインマージンを回復することが可能です。理想的には、位相整合の取れた高品質のケーブルを常に使用するのが最善ですが、プローブの負荷や、ケーブル、アダプター、フィクスチャ、および場合によってはオシロスコープのフロントエンドのリターンロスや挿入損失を、内蔵補正ルーチンによって補正できれば、デザインの真の性能の把握が容易になります。

この2つのスクリーンショットは、高速信号を、短いケーブル(黄色の波形)と長いケーブル(緑の波形)で測定した結果です。長いケーブルはディエンベッドされ、この例では理想基準として用いられている短いケーブルの応答と比較されています。ケーブル損失によって失われたマージンのほとんどが、アイマージンの改善によって回復されているのがわかります。

RF信号解析

RFデザイナーは、変調技術の複雑化、周波数の上昇、帯域幅の拡大に伴うデザイン上の課題に常に直面しています。信号経路内のすべての要素は、全体としてのRF測定性能に影響します。ケーブル、カップラー、アッテネータなどのアクセサリによって、歪み、リターンロス、位相誤差といった非理想的な影響が信号経路に生じます。

長いトレースの周波数依存の減衰は、一般的にS/N比の問題の最大の原因の1つです。固定アッテネータのような単純なコンポーネントによる歪みでも、予想以上の信号劣化をもたらす可能性があります。アッテネータ、ケーブル、PCBトレースは、ディエンベディング技術を用いることで容易に補正できます。

ディエンベッドされた信号のシリアルトリガ/デコード

デザインの問題の根本原因を見つけるには、問題を再現し、トリガによって分離することから始めるのが普通です。高速プロトコルトリガ/デコードは、電気信号とプロトコルレイヤーの動作を相関させるために不可欠なツールです。オシロスコープのプロトコルデコーダーの信頼性を確保するには、信号全体の品質をディエンベディングなどによって改善することが役立ちます。

トリガの信頼性向上の鍵は、信号振幅の増加と、シグナリング特性全体の改善です。これにより、トリガ/デコードシステムによるビットとシンボルの検出がはるかに容易になります。従来のオシロスコープアーキテクチャでは、トリガピックオフが用いられています。このため、表示されるディエンベッドされた信号(ソフトウェア補正後)は、トリガ回路に入力される未補正の信号と一致しません。R&S®RTPでは、トリガシステムと収集システムが共通の経路を使用するため、表示される信号とトリガに使用される信号が一致します。このため、きわめて複雑な信号バスを測定する場合でも、トリガの信頼性がはるかに高まります。

例えば、USB3.0 Gen1信号は、チャネルの末端で測定されます。このため信号損失が大きくなりますが、機械的制約のためにやむを得ません。それでもプロトコル動作をデコードすることは可能ですが、ヒステリシスやレベル差のために、一部のデータが破損したり、同期が取れなかったりすることがあります。

チャネル損失の一部または全部に補正を適用することで、シリアルデコードの信頼性と一貫性を改善できます。

ディエンベディング後のUSB3.0 Gen1

DDRインタフェーステストの最適化

シグナルインテグリティーの課題のうち、ディエンベディングによって対処が容易になるものとしては、反射の除去も挙げられます。例えば、DDRメモリシステムを検証する場合、信号にアクセスするには、近くのビア、ピン、またはその他のアクセスポイントに直接接続するのが普通です。コンポーネントインターポーザーを使用すれば、信号アクセスが容易になり、ボール・グリッド・アレイ(BGA)接点からルーティングされる関連信号を利用することもできます。インターポーザーをディエンベッドすることで、フィクスチャの信号減衰と、インピーダンス不整合から生じる反射を除去することができます。