DDR3 메모리 읽기 및 쓰기 주기 트리거링

DDR 인터페이스의 신호 무결성 성능을 분석할 때에는 읽기와 쓰기 주기를 분리하는 것이 어려운 과제였습니다. 특히 아이 다이어그램을 실시간으로 재생성할 때 포괄적 트리거 기능이 필요합니다.

DDR 인터페이스의 신호 무결성 성능을 분석할 때에는 읽기와 쓰기 주기를 분리하는 것이 어려운 과제였습니다. 특히 아이 다이어그램을 실시간으로 재생성할 때 포괄적 트리거 기능이 필요합니다.

DDR 인터페이스의 신호 품질은 메모리 시스템을 안정적으로 작동하는 데 중요합니다. 데이터 아이 분석은 신호 무결성을 평가하는 데 일반적으로 사용되는 방법입니다. DDR 아키텍처는 각각 다른 시간 간격에 동일한 신호 트레이스에서 읽기 및 쓰기 주기가 발생하는 반이중 작동을 사용합니다. 엔지니어는 eye 분석의 읽기와 쓰기 주기를 구분하기 위해 데이터(DQ)의 위상 정렬 및 스트로브(DSQ) 신호를 살펴봅니다. 전용 트리거링을 사용하여 읽기/쓰기 주기를 구분하는 것은 쉽지 않을 수 있지만 장기간의 데이터에 대한 eye 분석을 수행하는 것은 가능합니다.

읽기/쓰기 주기

R&S®RTP High-Performance Oscilloscope에는 고급 트리거 기능이 탑재되어 있습니다. 고유 디지털 트리거 시스템의 A-B 시퀀스에서는 정밀 시간 지연과 최저 1ps 분해능으로 연속 2개 트리거 조건을 설정할 수 있습니다. 트리거 조건은 다른 채널의 Logic Qualifier와 결합될 수 있습니다. 또한 R&S®RTP-K19 Zone Trigger 옵션을 사용할 경우 사용자가 트리거 조건을 한정된 구역에서 시각적으로 정의하여 간단히 설정할 수 있습니다.

읽기/쓰기 주기

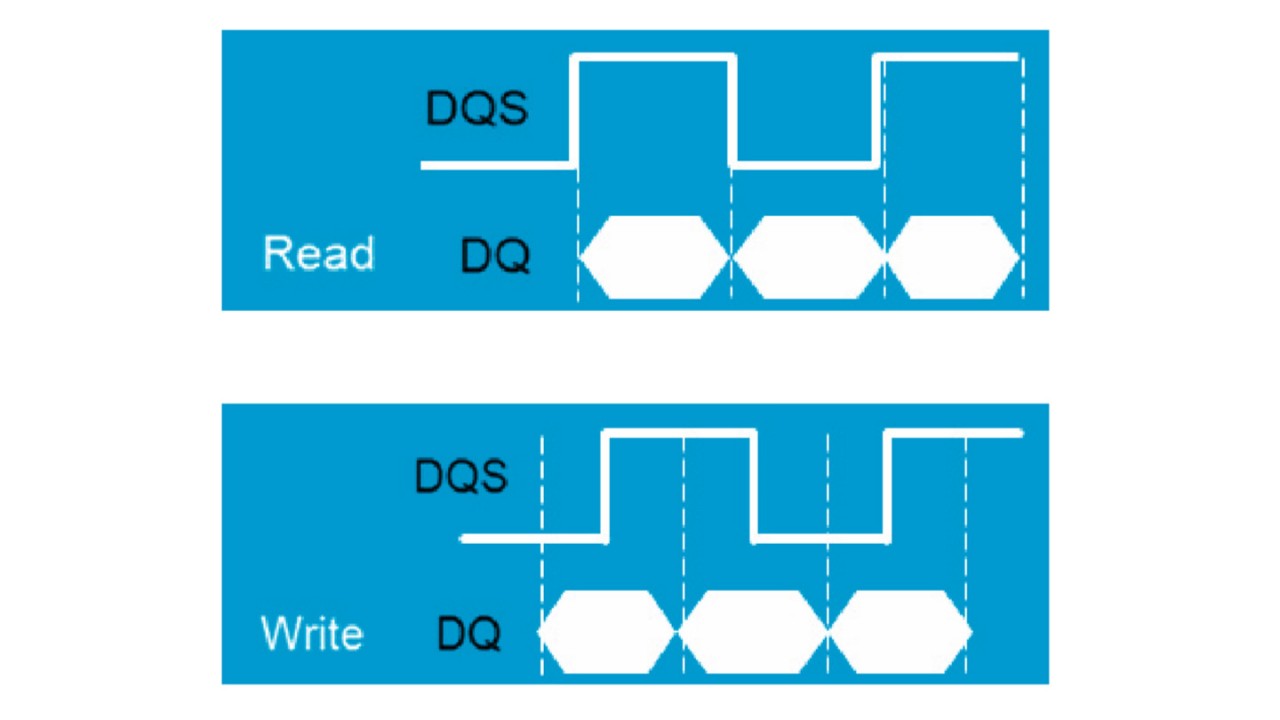

DDR 메모리 인터페이스는 읽기/쓰기 주기의 위상이 일치하지 않습니다. 이 아키텍처에서는 데이터가 안정적으로 높거나 낮을 때 데이터(DQ)를 래치하기 위해 메모리 컨트롤러가 DQS(Differential Strobe Signal)를 제공해야 합니다. 읽기 주기 중에는 DQS 및 DQ가 DRAM에서 메모리 컨트롤러로 동일 위상으로 전송되지만 쓰기 주기에서는 0.5 UI(Unit Interval) 오프셋이 있습니다.

지연이 있는 A-B 트리거 설정

쓰기 주기의 위상 관계를 활용하여 A 트리거 이벤트를 DQ 신호의 엣지 트리거로 정의할 수 있습니다. 그런 다음 지연 및 리셋 메커니즘이 DQS 신호에서 이벤트 B 엣지 트리거를 확인하기 위해 이를 제한합니다. 이벤트 B를 찾는 지연은 ½ UI 이내여야 합니다.

이벤트 A의 경우 3상 시퀀스에서 반환된 후 첫 번째 DQ 비트를 탐지하는 윈도우 트리거도 가능합니다(윈도우 폭 > 1 UI).

DQS 프리앰블에서 트리거

DDR3의 경우 DQS 프리앰블 비트는 쓰기 주기에서 양이며 읽기 주기에서 음입니다. DRAM 컨트롤러는 데이터 비트 폭에 비해 프리앰블 비트 폭이 약간 다릅니다. 이 차이를 기반으로 하는 트리거링이 가능합니다. 1 UI보다 긴 펄스에서 폭 트리거를 정의하거나 1 UI ~ 1.5 UI 범위를 사용할 수 있습니다. 프리앰블은 각각 다르게 구현되기 때문에 가장 먼저 기기의 프리앰블 타이밍 특성을 관찰하는 것이 좋습니다.

DQS 프리앰블에서 트리거

DDR3의 경우 DQS 프리앰블 비트는 쓰기 주기에서 양이며 읽기 주기에서 음입니다. DRAM 컨트롤러는 데이터 비트 폭에 비해 프리앰블 비트 폭이 약간 다릅니다. 이 차이를 기반으로 하는 트리거링이 가능합니다. 1 UI보다 긴 펄스에서 폭 트리거를 정의하거나 1 UI ~ 1.5 UI 범위를 사용할 수 있습니다. 프리앰블은 각각 다르게 구현되기 때문에 가장 먼저 기기의 프리앰블 타이밍 특성을 관찰하는 것이 좋습니다.

존 트리거

R&S®RTP는 특징적인 파형 형태를 기준으로 유효한 읽기 및 쓰기 주기를 한정하는 데 유효한 존 트리거(옵션)를 제공합니다. 화면에서 직접 존을 정의하여 신호가 존을 통과해야 하는지 여부를 구분할 수 있습니다. 이는 특히 파형 특성이 트리거 정의와 다를 경우 유용합니다.

쓰기 주기에서는 DQS와 DQ의 위상이 일치하지 않습니다. DQ 신호가 DQS와 동일한 엣지를 벗어나지 않도록 존을 정의할 수 있습니다.

DDR 메모리의 신호 무결성은 일반적으로 DRAM 측에서 측정합니다. 이는 쓰기 신호가 읽기 신호보다 전압 진폭이 낮음을 의미합니다. 따라서 존 영역은 신호 세기(전압 수준)를 기준으로 읽기 주기의 적합성 여부를 판단합니다.

DDR 메모리 인터페이스의 신호 무결성 평가에는 읽기 및 쓰기 주기를 안정적으로 구분하는 것이 중요합니다. R&S®RTP 고성능 오실로스코프의 디지털 트리거는 정밀한 순차 트리거 메커니즘을 보장합니다. 여기에 존 트리거를 결합할 경우 DDR 메모리 인터페이스 측정 시 유연하고 다양한 목적의 트리거링 기능을 제공할 수 있습니다.