Testing PCIe (peripheral component interconnect express)

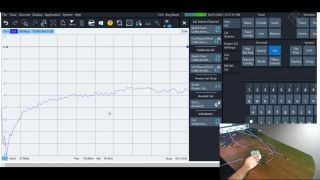

Practically all requirements for testing PCIe data transmissions and signal properties are met by oscilloscopes, both during development and for PCIe compliance test. On the physical layer, network analyzers can provide the highest possible precision for signal integrity test. With an automated network analyzer test setup only available from Rohde & Schwarz,dramatically reduce times for testing signal integrity parameters and increase test reliability for PCIe cables and connectors with four or more lanes, using the 5.0 or 6.0 specification.

PCIe is the de-facto standard for a server or PC mainboard interconnect, between the main processor and both integrated-peripherals (surface mounted chips) and plug-in peripherals (expansion cards) such as graphic cards or memory cards, or add-in boards. For PC manufacturers and chip and plug-in board suppliers throughout the industry, verifying PCIe interfaces during development, and subsequently for function verification and production quality control is an essential task.

First introduced in 2003 as PCIe 1.0 with a bandwidth of 8 GB/s running at a frequency of 2.5 GHz supporting 2.5 Giga transfers per second (GT/s), a new upgraded version has been released by the PCI-SIG (Special Interest Group) every couple of years, each time doubling the performance. The latest version released in 2022 is PCIe 6.0 with a bandwidth of 256 GB/s running at a frequency of 32 GHz supporting 64 GT/s. Data rates are shown as transfers per second, not the bit rate. This is due to the transmission coding converting data bits to a larger number of transmission characters in order to reduce transmission errors at the cost of an increased amount of information to transmit. For PCI 1.0 and 2.0 8b/10b coding is used, for 3.0 the transmission overhead is greatly reduced with 128b/130b coding. Transmission errors are reduced by achieving DC balance and bounded disparity (long term, 50% “1” and 50% “0” are transmitted).

While 128/130b reduces the protocol overhead from 25% to 1.5%, the protocol-based transmission error correction is also reduced. PCIe 3.0 added receiver equalization to compensate for in-channel frequency response at higher frequencies. Sophisticated algorithms aim to create digital filters matching the channel loss at the receiver.

PCIe connects by 1 or more lanes in a slot. A lane contains a transmit and receive pair of differential lines, so each lane is a full-duplex stream, transporting data packets. PCIe slots may contain from one to thirty-two lanes, in powers of two. Lane counts are written with an x prefix (e.g., x16 represents a sixteen-lane card or slot), with x16 being the largest size in common use. An x1 slot transmits data at 1 bit per cycle, an x16 slot at 16 bits per cycle. Both in terms of slots and versions PCIe is fully backwards compatible, with the data rate determined by the smaller slot size, and the lower version.

The commercial implementation of PCIe lags several versions behind the latest standard. There are still more 3.0 PC motherboards available than 4.0, which in turn outnumbers the 5.0 mother boards; the number of applications requiring data rates of more than 16 GT/s are strictly limited. For simpler processors running many industrial and commercial devices, PCIe 1.0 provides more than enough performance.