Teste de PCIe (interconexão expressa de componentes periféricos)

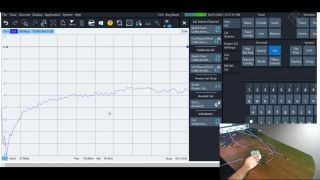

Praticamente todos os requisitos para testes de propriedades do sinal e transmissões de dados de PCIesão atendidos por osciloscópios, tanto durante o desenvolvimento quanto para testes de conformidade de PCIe. Na camada física, os analisadores de redespodem fornecer a maior precisão possível para o testes de integridade de sinal. Com uma configuração de testes para analisadores de redes automatizadosdisponível apenas na Rohde & Schwarz, reduz consideravelmente os tempos de testede parâmetros de integridade de sinal e aumenta a confiabilidade do testepara conectores e cabos PCIe com quatro ou mais pistas, usando a especificação 5.0 ou 6.0.

O PCIe é, de fato, o padrão para a interconexão de placa-mãe de computadores ou de um servidor, entre o processador principal e ambos os periféricos integrados (chips soldados na superfície) e os periféricos externos (placas de expansão), como placas de vídeo, cartões de memória, ou placas complementares. Para fabricantes de computadores e fornecedores de chips e placas de circuito impresso da indústria, a verificação de interfaces PCIeé uma tarefa essencial durante o desenvolvimento e, posteriormente, para a verificação da função e o controle de qualidade da produção.

Introduzido pela primeira vez em 2003 como PCIe 1.0, com uma largura de banda de 8 GB/s em uma frequência de 2,5 GHz, suportando 2,5 bilhões de transferências por segundo (GT/s), uma nova versão atualizadafoi lançada pela PCI-SIG(Grupo de Interesse Especial) a cada dois anos, e cada vez dobrando o desempenho. A versão mais recente, lançada em 2022, é o PCIe 6.0, com uma largura de banda de 256 GB/s, executada em uma frequência de 32 GHz com suporte a 64 GT/s. As velocidades de transmissão de dados são mostradas como transferências por segundo, não a taxa de bits. Isso se deve ao fato da codificação da transmissão converter os bits de dados em um número maior de caracteres de transmissão para reduzir os erros de transmissão ao custo de uma quantidade maior de informações a serem transmitidas. Para a PCI 1.0 e 2.0, é usada a codificação 8b/10b; para a 3.0, a sobrecarga de transmissão é reduzida de forma considerável com a codificação 128b/130b. Os erros de transmissão são reduzidos com o equilíbrio de corrente contínua e a disparidade limitada (a longo prazo, 50% « 1 » e 50% « 0 » são transmitidos).

Enquanto o 128/130b reduz o overhead do protocolo de 25% para 1,5%, a correção de erros de transmissão baseada em protocolo também é reduzida. O PCIe 3.0 adicionou a equalização do receiver para compensar a resposta de frequência no canal em frequências mais altas. Algoritmos sofisticados visam criar filtros digitais que coincidam com a perda de canal no receptor.

O PCIe se conecta por uma ou mais pistas em um slot. Uma pista contém um par de linhas diferenciais de recepção e transmissão, de modo que cada pista é um fluxo full-duplex, transportando pacotes de dados. Os slots PCIe podem conter de uma a trinta e duas pistas, em potências de dois. As contagens de pistas são escritas com um prefixo x (por exemplo, x16 representa uma placa ou slot de dezesseis pistas), sendo x16 o maior tamanho em uso comum. Um slot x1 transmite dados a 1 bit por ciclo e um slot x16 a 16 bits por ciclo. Tanto em termos de slots quanto de versões, o PCIe é totalmente compatível com versões anteriores, com a velocidade de transmissão de dados determinada pelo tamanho menor do slot, e a versão inferior.

A implementação comercial do PCIe está várias versões atrasada em relação ao padrão mais recente. Ainda há mais placas-mãe para PCIe 3.0 disponíveis do que 4.0, que, por sua vez, possui uma quantidade de placas-mãe que supera a da versão 5.0; o número de aplicações que exigem velocidades de transmissão de dados superiores a 16 GT/s é muito baixo. Para processadores mais simples que executam muitos dispositivos industriais e comerciais, o PCIe 1.0 oferece um desempenho mais do que suficiente.