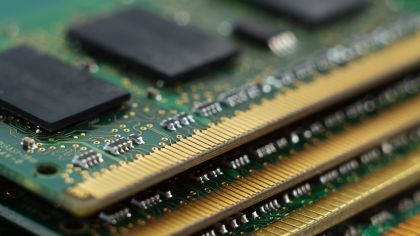

Test de la mémoire DDR

Comme c'est généralement le cas avec un bus de données série haut débit, les oscilloscopes peuvent gérer virtuellement tous les besoins en termes de test de débit de données double (DDR)de transferts de données et de propriétés du signal, à la fois au cours du développement et pour le test de conformité DDR. Sur la couche physique, les analyseurs de réseaux peuvent fournir le niveau de précision le plus élevé pour le test d'intégrité du signal. Il est crucial pour les fabricants d'ordinateurs et de tous types d'appareils électroniques qui utilisent la RAM (Random Access Memory) pour exécuter les programmes, ainsi que pour les fournisseurs de puces mémoire de l'industrie afin de mener un test de mémoire DDRau cours de la conception et ultérieurement pour la vérification fonctionnelle DDRet le contrôle qualité en production.

Les bases de la DDR

La technologie DDRpour le transfert de mémoire vers et à partir d'un processeur a été introduite en 1998 et en est dorénavant à sa cinquième génération. DDR est le raccourci pour débit de données “double”; car il y a deux transferts de mémoire par cycle d'horloge. Précédemment, il n'y en avait qu'un, ainsi la DDR a rapidement remplacé la SDRAM, ou Synchronous Dynamic Random Access Memory. La DDR domine à présent l'accès mémoire en lecture / écriture pour tous les types de petits processeurs et ordinateurs. Avec chaque génération de la DDR, les débits des transferts de données et les fréquences d'horloge ont augmentés, alors que les tensions de fonctionnement et les consommations de puissance ont diminuées. L'énorme augmentation de la performance et le manque de compatibilité entre les générations signifient que plusieurs générations de DDR sont utilisées – de la DDR5, introduite dans des PC de pointe en 2021, jusqu'à la DDR2, introduite en 2003. Alors que les composants DDR2 sont encore vendus en grandes quantités car ils existe de nombreux processeurs utilisant cette technologie, un nouveau développement est strictement limité.