PCIe(Peripheral Component Interconnect-Express)のテスト

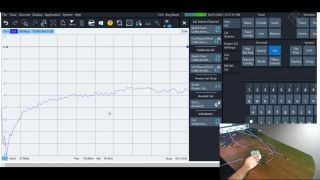

データ伝送や信号プロパティに関するPCIeテストの要件は、事実上すべてオシロスコープによって満たすことができます。これは、開発段階でもPCIeコンプライアンステストでも同じです。物理層については、ネットワーク・アナライザを使うことで、最高精度のシグナルインテグリティーテストが可能です。ローデ・シュワルツ独自の自動ネットワーク・アナライザテストセットアップを使えば、シグナルインテグリティーパラメータのテスト時間を大幅に短縮し、5.0または6.0仕様を使用する4レーン以上のPCIeケーブルやコネクタのテストの信頼性を向上させることができます。

PCIeは、サーバーやPCのメインボードのインターコネクトの業界標準であり、メインプロセッサと、内蔵周辺機器(表面実装チップ)およびグラフィックカードやメモリカード、アドインボードなどのプラグイン周辺機器(拡張カード)の両方の間をつなぐ役割を果たします。業界のすべてのPCメーカーやチップ/プラグインボードのサプライヤにとって、PCIeインタフェースの検証は、開発段階で、そしてその後の機能検証や製造品質管理のために、きわめて重要な作業です。

2003年に最初に発表されたPCIe 1.0は、帯域幅が8 GB/s、動作周波数が2.5 GHzで、2.5ギガ転送/秒(GT/s)をサポートしていました。その後、新しいアップグレードされたバージョンが、PCI-SIG(Special Interest Group)によって2、3年ごとにリリースされ、そのたびに性能が2倍になってきました。2022年にリリースされた最新バージョンのPCIe 6.0は、帯域幅が256 GB/s、動作周波数が32 GHzで、64 GT/sをサポートします。データレートは1秒あたりの転送回数で表されます。ビットレートではありません。これは、伝送コード化により、データビットがより多くの数の伝送キャラクターに変換されるからです。これにより、伝送する情報量が増える代わりに、伝送エラーを減らすことができます。PCI 1.0および2.0では8b/10bコード化が用いられ、3.0では128b/130bコード化により伝送オーバーヘッドが大幅に減少しています。伝送エラーの減少は、DCバランスと有界ディスパリティ(長期的には50 %の1と50 %の0が伝送される)の達成を通じて実現されます。

128/130bでは、プロトコルオーバーヘッドが25 %から1.5 %に減少する一方で、プロトコルベースの伝送エラー訂正も減少します。PCIe 3.0では、高い周波数でのインチャネル周波数応答を補正するために、レシーバーイコライゼーションが追加されました。高度なアルゴリズムにより、レシーバーでのチャネル損失に一致するデジタルフィルターの作成が試みられます。

PCIeの接続には、スロット内の1つまたは複数のレーンが使用されます。1つのレーンは、送信用と受信用の差動ラインのペアから構成されるので、各レーンが全2重のストリームであり、データパケットを伝送します。PCIeスロットは1~32のレーンを含むことができ、レーンの数は2のべき乗となります。レーン数はxを前に付けて表され(例:x16は16レーンのカードまたはスロット)、一般的な用途ではx16が最大のサイズです。x1スロットは1サイクルあたり1ビットのデータを伝送し、x16スロットは1サイクルあたり16ビットのデータを伝送します。スロットとバージョンの両方に関して、PCIeは完全な後方互換性があり、データレートは小さい方のスロットサイズと小さい方のバージョンによって決まります。

商用のPCIe実装は、最新規格から数バージョン遅れています。市販の3.0のPCマザーボードの数は現在でも4.0より多く、4.0のほうが5.0のマザーボードよりも一般的です。16 GT/sを超えるデータレートを要求するアプリケーションの数はきわめて制限されています。多くの産業用/商用デバイスに搭載されているシンプルなプロセッサにとって、PCIe 1.0の性能は十分以上です。